Advantech PCIE-1816 handleiding

Handleiding

Je bekijkt pagina 28 van 62

PCIE-1816_1816H User Manual 22

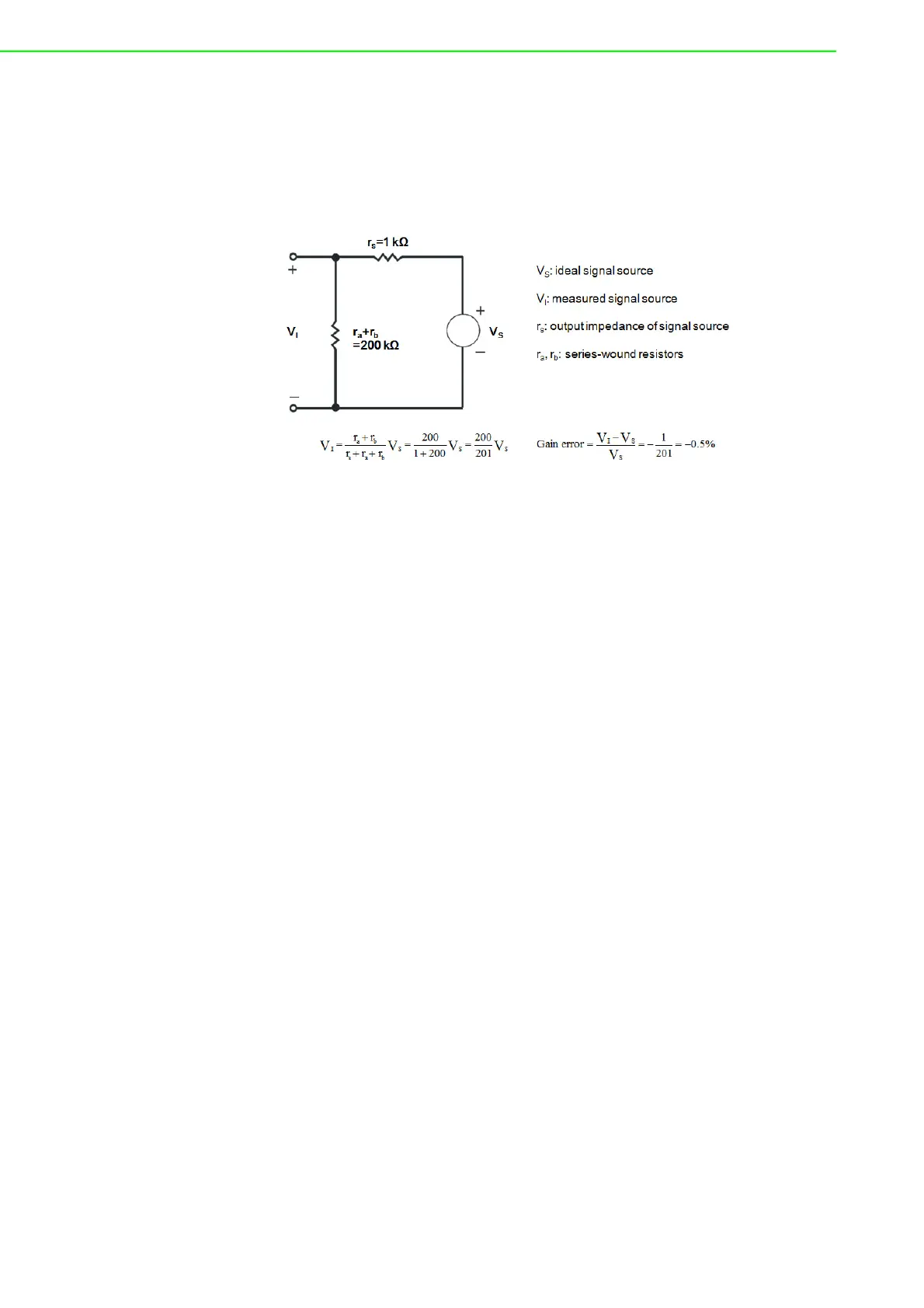

However, this connection has the disadvantage of loading the source down with the

series combination (sum) of the two resistors. For ra and rb, for example, if the input

impedance rs is 1k Ohm, and each of the two resistors is 100k Ohm, then the resis-

tors load down the signal source with 200 Ohm (100 Ohm+ 100 Ohm), resulting in a -

0.5% gain error. The following gives a simplified representation of the circuit and cal-

culating process.

AI Sample Clock Sources Connections

Internal AI Sample Clock

The internal AI sample clock uses a 100 MHz time base. Conversions start on the ris-

ing edge of the counter output. You can use software to specify the clock source as

internal and the sampling frequency to pace the operation. The minimum frequency

is 0.024 S/s, the maximum frequency is 500 KS/s. According to the sampling theory

(Nyquist Theorem), you must specify a frequency that is at least twice as fast as the

input’s highest frequency component to achieve a valid sampling. For example, to

accurately sample a 20 kHz signal, you have to specify a sampling frequency of at

least 40 kHz. This consideration can avoid an error condition often know as aliasing,

in which high frequency input components appear erroneously as lower frequencies

when sampling.

Bekijk gratis de handleiding van Advantech PCIE-1816, stel vragen en lees de antwoorden op veelvoorkomende problemen, of gebruik onze assistent om sneller informatie in de handleiding te vinden of uitleg te krijgen over specifieke functies.

Productinformatie

| Merk | Advantech |

| Model | PCIE-1816 |

| Categorie | Niet gecategoriseerd |

| Taal | Nederlands |

| Grootte | 9278 MB |