Advantech MIC-3332 handleiding

Handleiding

Je bekijkt pagina 52 van 62

MIC-3332 User Manual 42

C.1 Overview

For the MIC-3332 project, a CPLD (10M02SCU169I7G) from the Altera Max 10 fam-

ily is used.

C.1.1 CPLD Functional Blocks

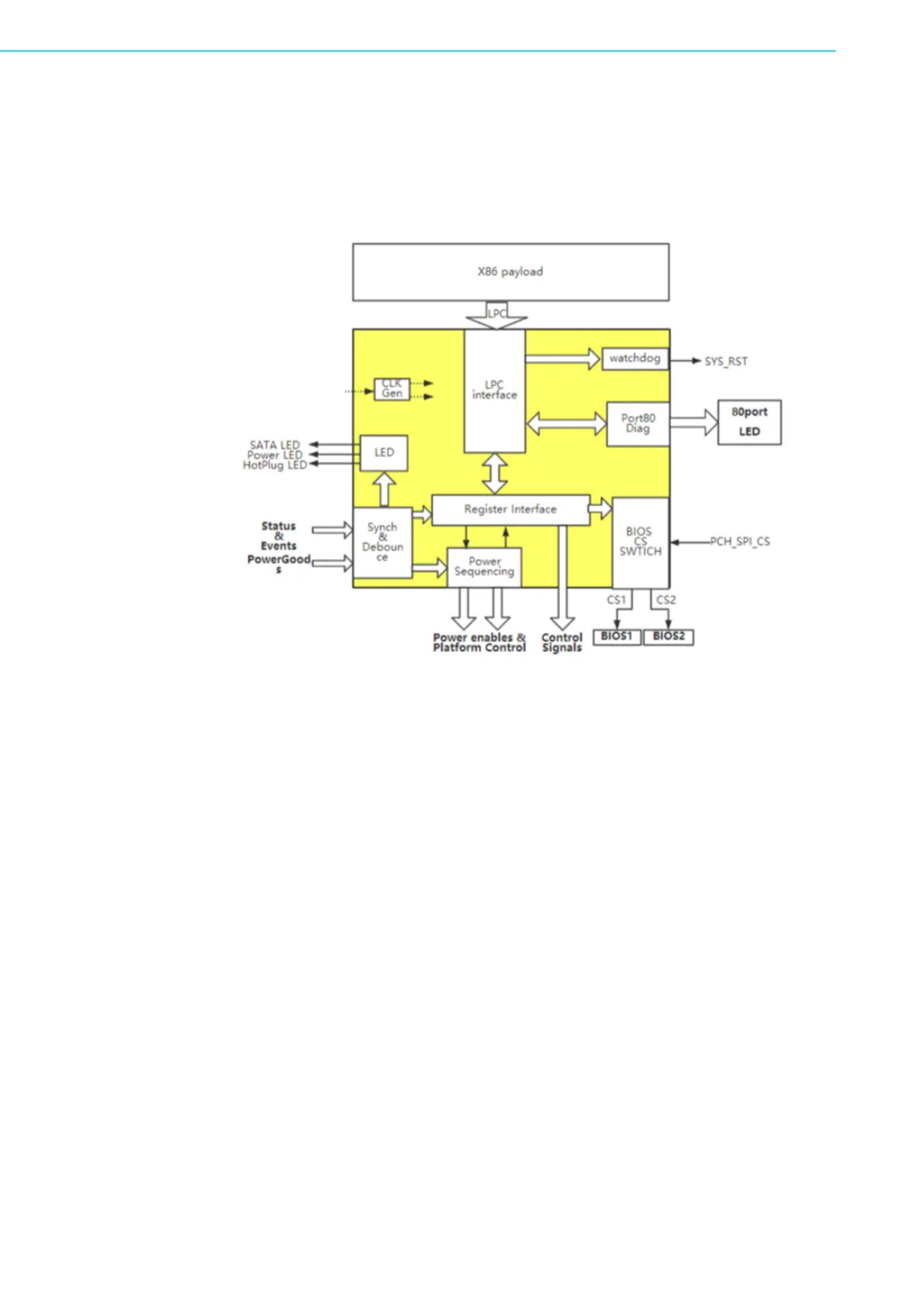

Figure C.1 CPLD Block Diagram

C.2 Features

The following functional blocks are realized inside the CPLD:

LPC interface

– Connects the LPC bus to the CPLD internal logic, Port80 diagnostic interface

– Realized as an LPC target

• supports IO access

Clock Generator

– Derivate internal needed clocks and timing pulses from 50MHz CPLD base

clock

Watchdog

– Watchdog function can cause system reset

– It can be called by writing value to registers from the LPC interface

Port 80 Diag

– POST LED control

LED

– Indicates the current state of the system

Register interface

– Contains all control and state signals

Synchronizer and Debouncer

– Synchronizes all external signals into CPLD clock domain

– Debounces all input from switches and jumpers with mechanical contacts

Bekijk gratis de handleiding van Advantech MIC-3332, stel vragen en lees de antwoorden op veelvoorkomende problemen, of gebruik onze assistent om sneller informatie in de handleiding te vinden of uitleg te krijgen over specifieke functies.

Productinformatie

| Merk | Advantech |

| Model | MIC-3332 |

| Categorie | Niet gecategoriseerd |

| Taal | Nederlands |

| Grootte | 8943 MB |