Microchip MPF050TL handleiding

Handleiding

Je bekijkt pagina 17 van 102

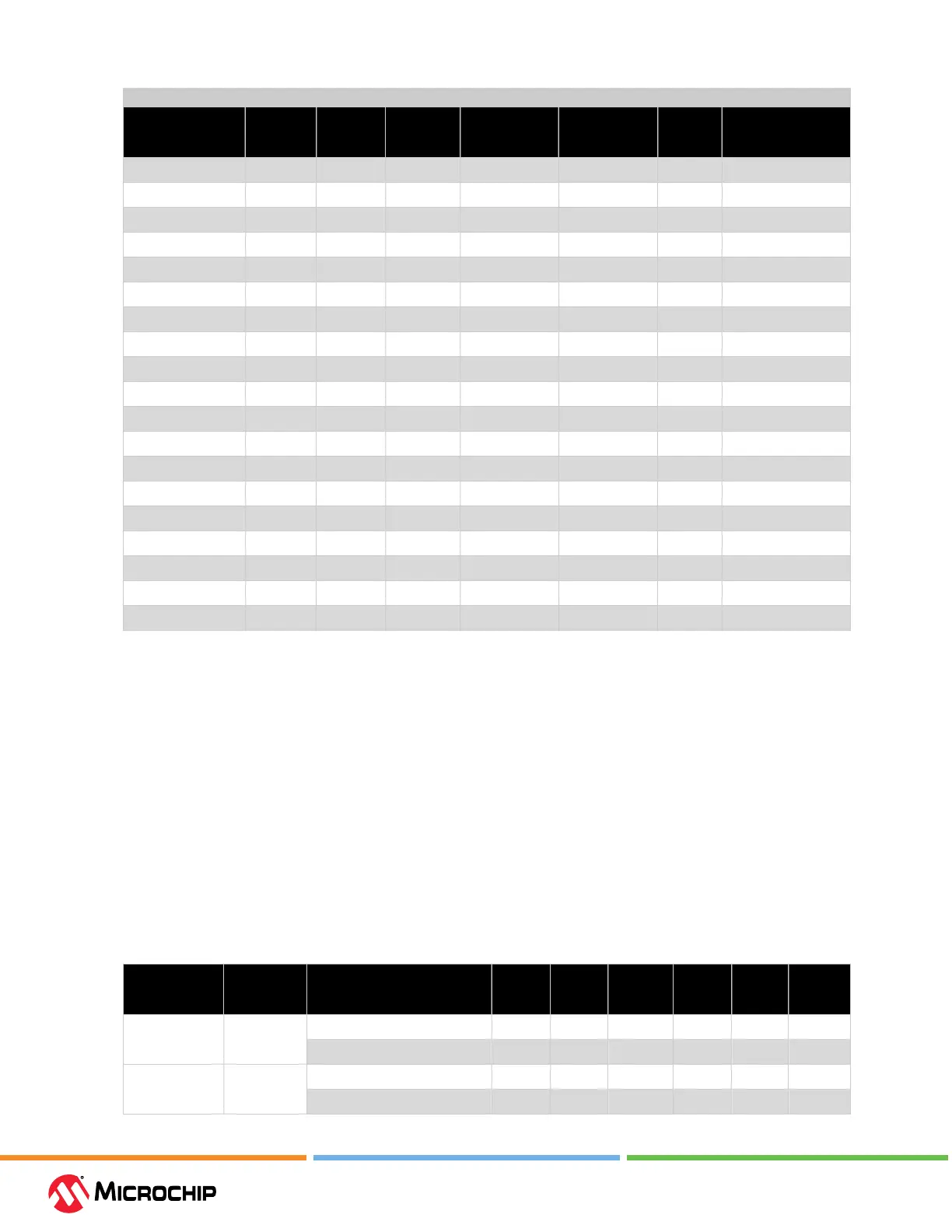

DC Characteriscs

Data Sheet

© 2024 Microchip Technology Inc. and its subsidiaries

DS00003831E - 17

...........continued

I/O Standard V

DDI

Min (V)

V

DDI

Typ (V)

V

DDI

Max (V)

V

OL

Max (V)

V

OH

Min (V)

I

OL

2,6

mA

I

OH

2,6

mA

SSTL25I

3

2.375 2.5 2.625 V

TT

– 0.608 V

TT

+ 0.608 8.1 8.1

SSTL25II

3

2.375 2.5 2.625 V

TT

– 0.810 V

TT

+ 0.810 16.2 16.2

SSTL18I

3

1.71 1.8 1.89 V

TT

– 0.603 V

TT

+ 0.603 6.7 6.7

SSTL18II

3

1.71 1.8 1.89 V

TT

– 0.603 V

TT

+ 0.603 13.4 13.4

SSTL15I

4

1.425 1.5 1.575 0.2 × V

DDI

0.8 × V

DDI

V

OL

/40 (V

DDI

– V

OH

)/40

SSTL15II

4

1.425 1.5 1.575 0.2 × V

DDI

0.8 × V

DDI

V

OL

/34 (V

DDI

– V

OH

)/34

SSTL135I

4

1.283 1.35 1.418 0.2 × V

DDI

0.8 × V

DDI

V

OL

/40 (V

DDI

– V

OH

)/40

SSTL135II

4

1.283 1.35 1.418 0.2 × V

DDI

0.8 × V

DDI

V

OL

/34 (V

DDI

– V

OH

)/34

HSTL15I 1.425 1.5 1.575 0.4 V

DDI

– 0.4 8 8

HSTL15II 1.425 1.5 1.575 0.4 V

DDI

– 0.4 16 16

HSTL135I

4

1.283 1.35 1.418 0.2 × V

DDI

0.8 × V

DDI

V

OL

/50 (V

DDI

– V

OH

)/50

HSTL135II

4

1.283 1.35 1.418 0.2 × V

DDI

0.8 × V

DDI

V

OL

/25 (V

DDI

– V

OH

)/25

HSTL12I

4

1.14 1.2 1.26 0.1 × V

DDI

0.9 × V

DDI

V

OL

/50 (V

DDI

– V

OH

)/50

HSTL12II

4

1.14 1.2 1.26 0.1 × V

DDI

0.9 × V

DDI

V

OL

/25 (V

DDI

– V

OH

)/25

HSUL18I

4

1.71 1.8 1.89 0.1 × V

DDI

0.9 × V

DDI

V

OL

/55 (V

DDI

– V

OH

)/55

HSUL18II

4

1.71 1.8 1.89 0.1 × V

DDI

0.9 × V

DDI

V

OL

/25 (V

DDI

– V

OH

)/25

HSUL12I

4

1.14 1.2 1.26 0.1 × V

DDI

0.9 × V

DDI

V

OL

/40 (V

DDI

– V

OH

)/40

POD12I

4,5

1.14 1.2 1.26 0.5 × V

DDI

— V

OL

/48 (V

DDI

– V

OH

)/48

POD12II

4,5

1.14 1.2 1.26 0.5 × V

DDI

— V

OL

/34 (V

DDI

– V

OH

)/34

1. Drive strengths per PCI specication V/I curves.

2. Refer to UG0686: PolarFire FPGA User I/O User Guide for details on supported drive strengths.

3. For external stub-series resistance. This resistance is on-die for GPIO.

4. I

OL

/I

OH

units for impedance standards in amps (not mA).

5. V

OH_MAX

based on external pull-up termination (pseudo-open drain).

6. The total DC sink/source current of all I/Os within a lane is limited as follows:

a. HSIO lane: 120 mA per 12 I/O buers.

b. GPIO lane: 160 mA per 12 I/O buers.

Note: 3.3V and 2.5V are only supported in GPIO banks.

4.3.2 Dierenal DC Input and Output Levels

The following tables list the dierential DC I/O levels.

Table 4-17. Dierenal DC Input Levels

I/O Standard Bank Type V

ICM_RANGE

Libero Setting V

ICM

1,3

Min (V)

V

ICM

1,3

Typ (V)

V

ICM

1,3

Max (V)

V

ID

2

Min (V)

V

ID

Typ (V)

V

ID

Max (V)

LVDS33 GPIO Mid (default) 0.6 1.25 2.35 0.1 0.35 0.6

Low 0.05 0.4 0.8 0.1 0.35 0.6

LVDS25

7

GPIO Mid (default) 0.6 1.25 2.35 0.1 0.35 0.6

Low 0.05 0.4 0.8 0.1 0.35 0.6

Bekijk gratis de handleiding van Microchip MPF050TL, stel vragen en lees de antwoorden op veelvoorkomende problemen, of gebruik onze assistent om sneller informatie in de handleiding te vinden of uitleg te krijgen over specifieke functies.

Productinformatie

| Merk | Microchip |

| Model | MPF050TL |

| Categorie | Niet gecategoriseerd |

| Taal | Nederlands |

| Grootte | 18409 MB |